两个D触发器级联实现四分频电路,原理:来一个时钟脉冲,D端数据就被送到输出端Q,同时输出一个反向数据到Q非端,下一个时钟脉冲到,重复上面过程,但数据己被取反,由此每两个时钟,Q端数被取反一次,由此得到二份频,...

”Quartus触发器 分频电路“ 的搜索结果

初步学习Quartus软件时,了解各种触发器的机理、用软件进行仿真,看波形图。

两个D触发器级联实现四分频电路,原理:来一个时钟脉冲,D端数据就被送到输出端Q,同时输出一个反向数据到Q非端,下一个时钟脉冲到,重复上面过程,但数据己被取反,由此每两个时钟,Q端数被取反一次,由此得到二份频,...

将D触发器的D端连接D触发器的输出QN端,就构成了一个由D触发器形成的2分频电路。多个D触发器级联得到4、8、16分频。 代码如下所示: module D_ff_4div(clkin,reset_n,clkout); input clkin,reset_n; output ...

一开始我觉得会比较困难,因为要设计D触发器,然后再利用D触发器去做二分频,在看了大家的博客设计完D触发器后,我发现!!!

要使用Quartus II设计一个4分频电路,我们可以使用D触发器来实现。首先,需要创建一个时钟信号,并确定它的频率。然后,使用一个D触发器和适当的逻辑电路连接。 1. 首先,打开Quartus II软件,创建一个新的项目。 ...

Quartus中D触发器入门

标签: stm32

在电路中,触发器的输入与输出是有一个延迟的,并不是上升沿一来,输出端马上输出数据,这是由于触发器内部电路决定的。 就算是最简单的非门,输入与输出也有延迟,更别说复杂的电路了。 如果我们是理想情况下,没有...

目录一、创建工程二、创建...启动分析与综合,确保无错,有错就更改电路图,直到无错为止 查看硬件电路图 创建波形文件 设置参数 效果 输入clk信号 设置D信号 选择部分区域设置为1 最后就是时序波形仿真 ...

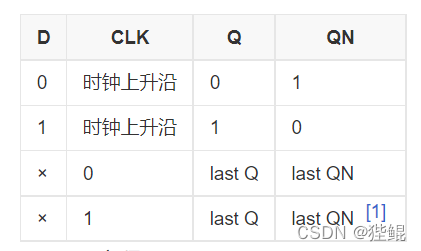

一、D触发器简介 D触发器是一种最简单的触发器,在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。在两个有效的脉冲边沿之间,D的跳转不会影响触发器存储的值,但是在脉冲边沿到来之前,输入...

文件名称: 04_div_clk_1Hz下载 收藏√ [5 4 3 2 1]开发工具: VHDL文件大小: 3176 KB上传时间: 2015-11-08下载次数: 0提 供 者: 刘年详细说明:verilog HDL 描述分频电路 产生1Hz脉冲方波信号 系统时钟频率50MHz-this...

基于 FPGA 实现的分频电路一般有两种方法:一是使用FPGA 芯片内部提供的锁相环电路,如 ALTERA 提供的 PLL(Phase Locked Loop),Xilinx 提供的 DLL(Delay Locked Loop);二是使用硬件描述语言,如VHDL、Verilog ...

Quartu编写D触发器

标签: fpga开发

分频电路是数字电路中常见的逻辑电路类型。在时序逻辑电路中,时钟是必不可少的,但对于时钟要求不高的基本设计,自行设计的分频电路,也就是时钟分频器,有时候比采用外部PLL更为简单、有效、快速。本文将详细介绍...

推荐文章

- LTE无线网络覆盖优化与增强实践指南4.2-程序员宅基地

- ISP流程概述-程序员宅基地

- 堆取料机防碰撞系统促进港口物料搬运效率进行提档升级_港口取料机防碰撞方法-程序员宅基地

- SQLAlchemy 第一篇_sqlalchamy with-程序员宅基地

- linux装系统出现boot,Linux系统安装时提示boot efi 没有分配空间的解决办法-程序员宅基地

- 有关数仓增量和全量同步的一些思考_数据向数仓同步数据需要注意的-程序员宅基地

- python cookbook 中文版 第 3 版-《Python Cookbook》第三版中文版-程序员宅基地

- TCP、UDP、HTTP、HTTPS之前的区别-程序员宅基地

- 国内外物联网平台清单-物联网平台技术选型参考_leapiot platform-程序员宅基地

- gperf概念以及使用步骤-程序员宅基地